# COMMODORE SEMICONDUCTOR GROUP

a division of Commodore Business Machines, Inc. 950 Rittenhouse Road, Norristown, PA 19403 • 215/666-7950 • TWX 510-660-4168

# NMOS

# 6500/1 ONE-CHIP MICROCOMPUTER

#### INTRODUCTION

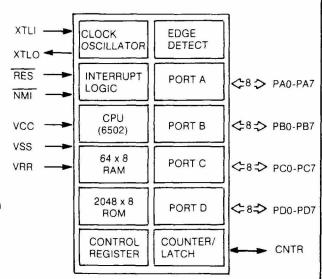

The 6500/1 is a complete, high-performance 8-bit NMOS microcomputer on a single chip, and is totally upward/downward software compatible with all members of the 6500 family.

The 6500/1 consists of a 6502 CPU, an internal clock oscillator, 2048 bytes of Read Only Memory (ROM), 64 bytes of Random Access Memory (RAM) and flexible interface circuitry. The interface circuitry includes a 16-bit programmable counter/latch with four operating modes, 32 bidirectional input/output lines (including two edge-sensitive lines), five interrupts and a counter I/O line.

#### **FEATURES**

- N-channel, silicon gate, depletion load technology

- 6502 CPU

- -Software upward/downward compatibility

- -Decimal or binary arithmetic modes

- -13 addressing modes

- -True direct and indirect indexing

- -Memory addressable I/O

- -Variable length stack

- 2048 x 8 mask programmable ROM

- 64 x 8 static RAM

- 32 bi-directional TTL compatible I/O lines (4 ports)

- —1 positive edge sensitive line

- -1 negative edge sensitive line

- 1 bi-directional TTL compatible counter I/O line with asynchronous operation in input mode

- 16-bit programmable counter/latch with four modes

- -Interval Timer

- -Event Counter

- -Pulse Generator

- -Pulse Width Measurement

- Five Interrupts

- -Reset

- -Two external edge sensitive

- -Non-maskable

- -Counter overflow

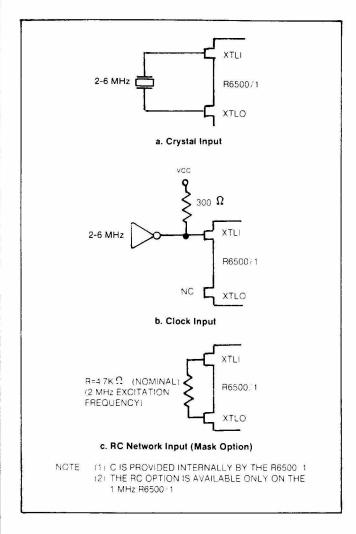

- 1 of 3 frequency references

- -Crystal —Clock

- -RC (resistor only)

- 1 to 3 MHz internal clock frequency (available in 100KHz intervals). 6 MHz max crystal or clock external frequency.

- Single +5V power supply

- · 1100 mW maximum operating power

- Separate power pin for RAM

- 40 pin DIP

- Compatible with R6500/1E Emulator

# INTERFACE DIAGRAM

## MASK PROGRAMMABLE OPTIONS

- Internal pull-up resistors on ports A, B, C, D. Selectable for 8-bit port groups only, not for individual port lines.

- Internal pull-up resistor on the CNTR line.

The RC frequency option is available Note: only in the 1 MHz 6500/1.

#### SIGNAL DESCRIPTIONS

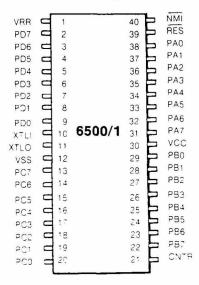

| Signal<br>Name | Pin<br>No. | Description                                                                                                                                                                                                |

|----------------|------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| VCC            | 30         | Main power supply + 5V                                                                                                                                                                                     |

| VRR            | 1          | Separate power pin for RAM. In the event that VCC power is lost, this power retains RAM data.                                                                                                              |

| VSS            | 12         | Signal ground                                                                                                                                                                                              |

| XTLI           | 10         | Crystal, clock or RC network input for internal clock oscillator.                                                                                                                                          |

| XTLO           | 11         | Crystal or RC network output from internal clock oscillator.                                                                                                                                               |

| RES            | 39         | The Reset input is used to initialize the 6500/1. This signal must not transition from low to high for at least eight cycles after VCC reaches operating range and the internal oscillator has stabilized. |

|                |            | + 10V input enables the test mode.                                                                                                                                                                         |

| NMI            | 40         | A negative going edge on the Non-Maskable Interrupt signal requests that a non-maskable interrupt be generated within the CPU.                                                                             |

| PA0-PA7        | 38-31      | Four 8 bit ports used for either                                                                                                                                                                           |

| PB0-PB7        | 29-22      | input/output. Each line consists of<br>an active transistor to VSS and a                                                                                                                                   |

| PC0-PC7        | 20-13      |                                                                                                                                                                                                            |

| PD0-PD7        | 9-2        | bits of the PA port (PA0 and PA1) also<br>serve as edge detect inputs with<br>maskable interrupts.                                                                                                         |

| CNTR           | 21         | This line is used as a Counter input/output line. CNTR is an input in the Event Counter and Pulse Width Measurement modes and is an output in the Interval Timer and Pulse Generator modes.                |

#### PIN CONFIGURATION

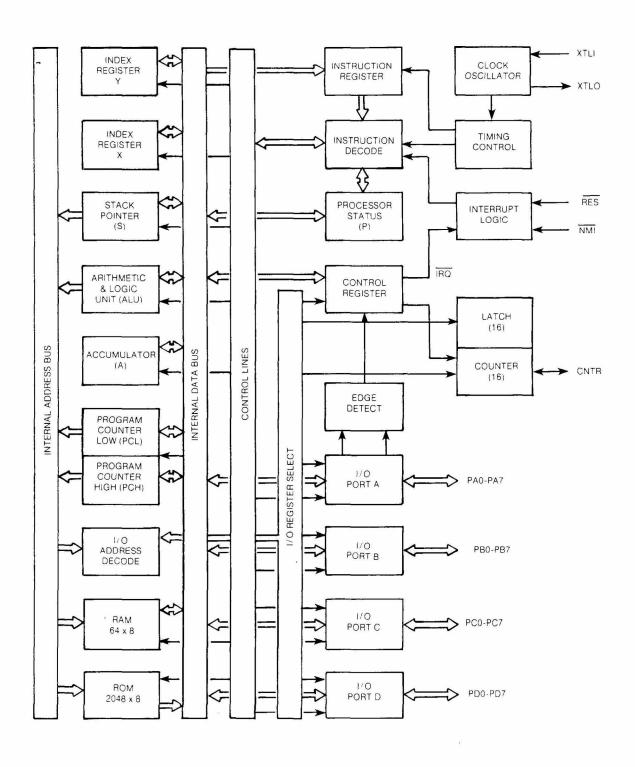

#### **FUNCTIONAL DESCRIPTION**

This section gives a functional description of the logic blocks as shown in the block diagram.

# **CENTRAL PROCESSING UNIT (CPU)**

#### Accumulator

The accumulator is a general purpose 8-bit register that stores the results of most arithmetic and logic operations. In addition, the accumulator usually contains one of the two data words used in these operations.

#### **Index Registers**

There are two 8-bit index registers, X and Y. These registers can be used for general purpose storage, or as a displacement to modify the base address and thus obtain a new effective address. Pre- or post-indexing of indirect addresses is possible.

#### **Stack Pointer**

The Stack Pointer is an 8-bit register. It is automatically incremented and decremented under control of the CPU to perform stack manipulation under direction of either the program or interrupts NMI and IRQ. The stack allows simple implementation of nested subroutines and multiple level interrupts.

#### Arithmetic and Logic Unit (ALU)

All arithmetic and logic operations take place in the ALU, including incrementing and decrementing internal registers (except the Program Counter). The ALU cannot store data for more than one cycle. If data are placed on the inputs to the ALU at the beginning of a cycle, the result is always gated into one of the storage registers or to external memory during the next cycle.

Each bit of the ALU has two inputs. These inputs can be tied to various internal buses or to a logic zero; the ALU then generates the function (AND, OR, SUM, and so on) using the data on the two inputs.

#### **Timing Control**

The Timing Control Logic keeps track of the specific instruction cycle being executed. Each data transfer which takes place between the registers is caused by decoding the contents of both the Instruction Register and Timing Control Logic.

#### Instruction Register and Decode

Instructions fetched from memory are gated onto the Internal Data Bus. These instructions are latched into the Instruction Register then deocoded, along with timing and interrupt signals, to generate control signals for the various registers.

# 6500/1 BLOCK DIAGRAM

#### **Clock Oscillator**

The Clock Oscillator provides the basic timing signals used by the 6500/1 CPU. The reference frequency is provided by an external source, and can be from a crystal. clock or RC network input. The RC network mode is a mask option. The external frequency can vary from 200 KHz to 6 MHz. The internal Phase 2 (Ø2) frequency is one-half the external reference frequency. A 4.7K ohm resistor will provide nominal 2 MHz oscillation and 1 MHz internal operation in the RC mask option (+ 35%).

#### Interrupt Logic

Interrupt logic controls the sequencing of three interrupts: RES, NMI and IRQ. IRQ is generated by any one of three conditions: Counter Overflow, PA0 Positive Edge Detected, and PA1 Negative Edge Detected. Multiple simultaneous interrupts on IRQ will cause the request to remain active until all interrupt conditions have been serviced and cleared.

#### **Program Counter**

The 16-bit Program Counter provides the addresses which step the CPU through sequential instructions in a program. The Program Counter is incremented each time an instruction or data is fetched from memory.

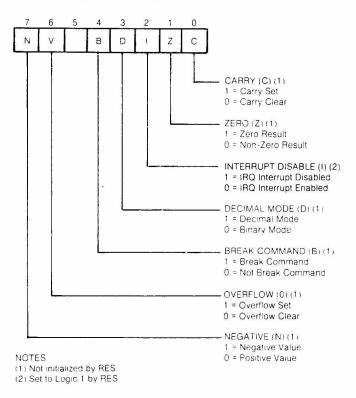

#### **Processor Status Register**

The 8-bit Processor Status Register contains seven status flags. Some of the flags are controlled by the program, others may be controlled both by the program and the CPU. The 6500 instruction set contains a number of conditional branch instructions which are designed to allow testing of these flags.

#### Carry Bit (C)

The Carry Bit (C) can be considered as the ninth bit of an arithmetic operation. It is set to logic 1 if a carry from the eighth bit has occurred or cleared to logic 0 if no carry occurred as the result of arithmetic operations.

The Carry Bit may be set or cleared under program control by use of the Set Carry (SEC) or Clear Carry (CLC) instruction. respectively. Other operations which affect the Carry Bit are ADC. ASL. CMP, CPX, CPY, LSR, PLP, ROL, ROR, RTI, and SBC.

#### Zero Bit (Z)

The Zero Bit (Z) is set to logic 1 by the CPU during any data movement or calculation which sets all 8 bits of the result to zero. This bit is cleared to logic 0 when the resultant 8 bits of a data movement or calculation operation are not all zero. The 6500/1 instruction set

contains no instruction to specifically set or clear the Zero Bit. The Zero Bit is, however, affected by the following instructions: ADC. AND, ASL, BIT, CMP, CPX, CPY, DEC, DEX, DEY, EOR, INC, INX, INY, LDA, LDX, LDY, LSR, ORA, PLA, PLP, ROL, ROR, RTI, SBC, TAX, TAY, TXA, TSX, AND TYA.

#### Interrupt Disable Bit (I)

The Interrupt Disable Bit (I) is used to control the servicing of an interrupt request (IRQ). If the I Bit is reset to logic 0, the IRQ signal will be serviced. If the bit is set to logic 1, the IRQ signal will be ignored. The CPU will set the Interrupt Disable Bit to logic 1 if a RESET (RES) or Non-Maskable Interrupt (NMI) signal is detected.

The I bit is cleared by the Clear Interrupt (CLI) instruction, the Pull Processor Status from Stack (PLP) instruction, or as the result of executing a Return from Interrupt (RTI) instruction (providing the Interrupt Disable Bit was cleared prior to the interrupt). The Interrupt Disable Bit may be set or cleared under program control using a Set Interrupt Disable (SEI) or a Clear Interrupt Disable (CLI) instruction, respectively.

# Decimal Mode Bit (D)

The Decimal Mode Bit (D), is used to control the arithmetic mode of the CPU. When this bit is set to logic 1, the adder operates as a decimal adder. When this bit is cleared to logic 0, the adder operates as a straight binary adder. The adder mode is controlled only by the programmer. The Set Decimal Mode (SED) Instruction will set the D bit; the Clear Decimal Mode (CLD) Instruction will clear it. The PLP and RTI Instructions also effect the Decimal Mode Bit.

# CAUTION

The Decimal Mode Bit will either set or clear in an unpredictable manner upon power application to R6500/1. This bit must be initialized to the desired state by the user program or erroneous results may occur.

# Break Bit (B)

The Break Bit (B) is used to determine the condition which caused the IRQ service routine to be entered. If the IRQ service routine was entered because the CPU executed a BRK command, the Break Bit will be set to logic 1. If the IRQ routine was entered as the result of an IRQ signal being generated, the B bit will be cleared to logic 0. There are no instructions which can set or clear this bit.

#### Overflow Bit (V)

The Overflow Bit (V) is used to indicate that the result of a signed, binary addition, or subtraction, operation is a value that cannot be contained in seven bits (-128 n 127). This indicator only has meaning when signed arithmetic (sign and seven magnitude bits) is performed.

When the ADC or SBC instruction is performed, the Overflow Bit is set to logic 1 if the polarity of the sign bit (bit 7) is changed because the result exceeds + 127 or -128; otherwise the bit is cleared to logic 0. The V bit may also be cleared by the programmer using a Clear Overflow (CLV) instruction.

The Overflow Bit may also be used with the BIT Instruction. The BIT Instruction which may be used to sample interface devices, allows the overflow flag to reflect the condition of bit 6 in the sampled field. During a BIT Instruction the Overflow Bit is set equal to the content of the bit 6 on the data tested with BIT Instruction. When used in this mode, the overflow has nothing to do with signed arithmetic, but is just another sense bit for the microprocessor. Instructions which affect the V flag are ADC, BIT, CLV, PLP, RTI and SBC.

# Negative Bit (N)

The Negative Bit (N) is used to indicate that the sign bit (bit 7), in the resulting value of a data movement or data arithmetic operation, is set to logic 1. If the sign bit is set to logic 1, the resulting value of the data movement or arithmetic operation is negative; if the sign bit is cleared, the result of the data movement or arithmetic operation is positive. There are no instructions that set or clear the Negative Bit since the Negative Bit represents only the status of a result. The Instructions that effect the state of the Negative Bit are: ADC, AND, ASL, BIT, CMP, CPX, CPY, DEC, DEX, DEY, EOR, INC, INX, INY, LDA, LDX, LDY, LSR, ORA, PLA, PLP, ROL, ROR, RTI, SBC, TAX, TAY, TSX, TXA, and TYA.

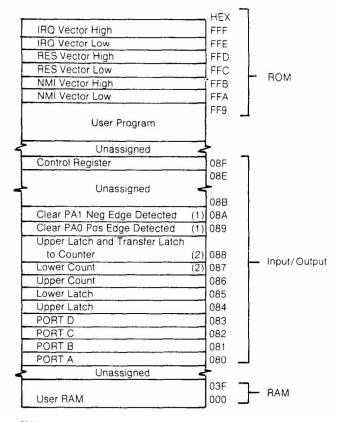

#### **MEMORY**

# 2048 x 8 ROM

The 2048 byte Read-Only Memory (ROM) contains the program instructions and other fixed constants. These program instructions and constants are mask programmed into the ROM during fabrication of the 6500/1 device. The 6500/1 ROM is memory mapped from 800 to FFF.

#### 64 x 8 RAM

The 64 byte Random Access Memory (RAM) is used for read/write memory during system operation, and contains the stack. This RAM is completely static in operation and requires no clock or dynamic refresh. A standby power pin, VRR, allows RAM memory to be maintained on 10% of the operating power in the event that VCC power is lost.

In order to take advantage of efficient zero page addressing capabilities, the RAM is assigned memory addresses 0 to 03F.

#### INPUT/OUTPUT

#### Bidirectional I/O Ports

The 6500/1 provides four 8-bit input/output ports (PA, PB, PC, and PD). Associated with the I/O ports are four 8-bit registers located on page zero. See the system memory map for specific addresses. Each I/O line is individually selectable as an input or an output without line grouping or port association restrictions.

An internal active transistor drives each I/O line to the low state. An internal passive resistance pulls the I/O lines to the high state, eliminating the need for external pull-up resistors.

An option is available to delete the internal pull-up resistance on 8-bit port groups or on the CNTR line at mask time. This option is employed to permanently assign an 8-bit port group to input functions, to interface with CMOS drivers, or to interface with external pull-up devices.

#### Inputs

Inputs are enabled by setting the appropriate bit of the I/O port to the high state (Logic 1). A low input signal causes a logic 0 to be read. A high input signal causes a logic 1 to be read. RES loads Logic 1 into the I/O ports, thereby initializing all I/O lines as inputs.

## Outputs

Outputs are set by loading the desired bit pattern into corresponding I/O ports. A Logic 1 selects a high output; a Logic 0 selects a low output.

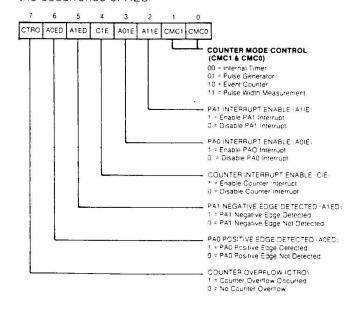

#### **CONTROL REGISTER**

The Control Register (CR), located at address 08F, controls four Counter operating modes and three maskable interrupts. It also reports the status of three interrupt conditions. There are five control bits and three status bits. The control bits are set to Logic 1 or cleared to Logic 0 by writing the desired state into the respective bit positions. The Control Register is cleared to Logic 0 by the occurrence of RES.

#### **EDGE DETECT CAPABILITY**

There is an asynchronous edge detect capability on two of the Port A I/O lines. This capability exists in addition to and independently from the normal Port A I/O functions. The maximum rate at which an edge can be detected is one-half the Ø2 clock rate. The edge detect logic is continuously active. Each edge detect signal is associated with a maskable interrupt.

# **PA0 Positive Edge Detection**

A positive (rising) edge is detectable on PA0. When this edge is detected, the PA0 Positive Edge Detected bit—Bit 6 in the Control Register—is set to Logic 1. When both this bit and the PA0 Interrupt Enable Bit—Bit 3 of the Control Register—are set to Logic 1, an IRQ interrupt request is generated. The PA0 Positive Edge Detected bit is cleared by writing to address 089.

The edge detecting circuitry is active when PA0 is used either as an input or as an output. When PA0 is used as an output, A0ED will be set when the positive edge is detected during a logical 0 to 1 transition.

When PA0 is used as an input and the positive edge detecting circuitry is used, A0ED should be cleared by the user program upon initialization and upon completion of PA0 Positive Edge Detected IRQ processing.

#### **PA1 Negative Edge Detection**

A negative (falling) edge is detectable on PA1. When this edge is detected, the PA1 Negative Edge Detected bit—Bit 5 of the Control Register—is set to Logic 1. When both this bit and the PA1 Interrupt Enable bit—Bit 2 of the Control Register—are set to Logic 1, an IRQ interrupt request is generated. The PA1 Negative Edge Detected bit is cleared by writing to address 08A.

The edge detecting circuitry is active when PA1 is used either as an input or as an output. When PA1 is used as an output. A1ED will be set when the negative edge is detected during a logical 1 to 0 transition.

When PA1 is used as an Input and the negative edge detecting circuitry is used, A1ED should be cleared by the user program upon initialization and when the PA1 Negative Edge Detected IRQ processing is completed.

#### COUNTER/LATCH

The Counter/Latch consists of a 16-bit decrementing Counter and a 16-bit Latch. The Counter is comprised of two 8-bit registers. Address 086 contains the Upper Count (UC) and address 087 contains the Lower Count (LC). The Counter counts either Ø2 clock periods or occurrences of an external event, depending on the selected counter mode. The UC and LC can be read at any time without affecting counter operation.

The Latch contains the Counter preset value. The Latch consists of two 8-bit registers. Address 084 contains the Upper Latch (UL) and address 085 contains the lower latch (LL). The 16-bit Latch can hold a count from 0 to 65.535. The Latch can be accessed as two write-only memory locations.

The Latch registers can be loaded at any time by storing into UL and LL. The UL can also be loaded by writing into address 088.

The Counter can be preset at any time by writing to address 088. Presetting the Counter in this manner causes the contents of the accumulator to be stored into the UL before the 16-bit value in the Latch (UL and LL) is transferred in the Counter (UC and LC).

The Counter is preset to the Latch value when the Counter overflows. When the counter decrements from 0000, Counter overflow occurs causing the next counter value to be the Latch value, not FFFF.

When the Counter overflows, Counter Overflow bit—Bit 7 of the Control Register—is set to Logic 1. When both this bit and the Counter Interrupt Enable bit—Bit 4 of the Control Register—are set, an IRQ interrupt request is generated. The Counter Overflow bit in the Control Register can be examined in an IRQ interrupt service routine to determine that the IRQ was generated by Counter overflow.

#### COUNTER OVERFLOW

The Counter Overflow Bit is set to Logic 1 whenever a counter overflow occurs in any of the four counter operating modes. Overflow occurs when the counter is decremented one count from 0000. This bit is cleared to logic 0 by RES or by reading from addiess 087 or writing to address 088.

This bit should be cleared by the user program upon initialization and upon completion of Counter Overflow IRQ interrupt processing.

When a Counter Overflow occurs, the Upper Count (UC) in address 086 and the Lower Count (LC) in address 087 are reset to the values contained in the Upper Latch (UL) in address 084 and in the Lower Latch (LL) in address 085, respectively. Therefore, it is important to load the Lower Latch value prior to executing the Write to Upper Latch and Transfer Latch to Counter (address 088) in order to prevent an unpredicted reoccurrence of Counter Overflow and, if enabled, an IRQ interrupt request.

#### **COUNTER MODES**

The Counter operates in any of four modes. These modes are selected by the Counter Mode Control bits in the Control Register.

| Mode                    | CMC 1 | CMC 0 |

|-------------------------|-------|-------|

| Interval Timer          | 0     | 0     |

| Pulse Generator         | 0     | 1     |

| Event Counter           | 1     | 0     |

| Pulse Width Measurement | 1     | 1     |

The Interval Timer, Pulse Generator, and Pulse Width Measurement Modes are Ø2 clock counter modes. The Event Counter Mode counts the occurrences of an external event on the CNTR line.

#### Interval Timer (Mode 0)

In this mode the Counter is free running and decrements at the  $\emptyset$ 2 clock rate. Counter overflow sets the Control Register status bit and causes the Counter to be preset to the Latch value. The Counter is also preset to the latch value by performing a write operation to counter address 088.

The Counter value is decremented by one count at the  $\emptyset$ 2 clock rate. The 16-bit Counter can hold from 1 to 65535 counts. The Counter Timer capacity is therefore 1 us to 65.535ms at the 1 MHz  $\emptyset$ 2 clock rate or 0.5 us to 32.768ms at the 2 MHz  $\emptyset$ 2 clock rate. Time intervals greater than the maximum Counter value can be easily measured by counting  $\overline{IRQ}$  interrupt requests in the counter  $\overline{IRQ}$  interrupt routine.

While operated in this mode, the CNTR line is held in the high state.

### Pulse Generator (Mode 1)

In this mode the Counter is free running and decrements at the Ø2 clock rate. The Counter Out/Event In line (CNTR) operates as Counter Out. Counter overflow sets the Control Register status bit and causes the Counter to be preset to the Latch value.

The CNTR line toggles from one state to the other when Counter overflow occurs. Writing to address 088 will also toggle the CNTR line.

A symmetric or asymmetric output waveform can be generated on the CNTR line in this mode. A one-shot waveform can easily be generated by changing from Mode 1 to Mode 0 after only one occurrence of the output toggle condition.

#### **Event Counter (Mode 2)**

In this mode the CNTR line is used as an event input line. The Counter decrements each time a rising edge is detected on CNTR. The maximum rate at which this edge can be detected is one-half the Ø2 clock rate. Counter overflow sets the Control Register status bit and causes the Counter to be preset to the Latch value.

External events on the CNTR line may be fully asynchronous to the 6500/1 clock.

#### Pulse Width Measurement (Mode 3)

This mode allows the accurate measurement of the duration of a low state on the CNTR line. The Counter decrements at the Ø2 clock rate as long as the CNTR line is held in the low state. The Counter is stopped when CNTR is in the high state. If the CNTR pin is left disconnected, this mode may be selected to stop the Counter since the internal pull-up device will cause the CNTR input to be in the high state.

# **RESET CONSIDERATIONS**

The occurrence of RES going from low to high causes initialization of various conditions in the 6500/1. All of the I/O ports (PA, PB, PC, and PD) and CNTR are forced to the high (Logic 1) state. All bits of the Control Register are reset to Logic 0, causing the Interval Timer Mode (Mode 0) to be selected and all interrupt enabled bits to be cleared. Neither the Latch nor the Counter registers are initialized by RES. The Interrupt Disable bit in the CPU Processor Status Register is set and the program starts execution at the address contained in the Reset Vector location.

#### POWER ON/OFF TIMING

After application of VCC power to the R6500/1, RES must be held low for at least eight Ø2 clock cycles after VCC reaches operating range and the internal clock oscillator has stabilized. This stabilization time is dependent upon the input VCC voltage and performance of the crystal, clock, or RC network input circuit. The clock oscillator output can be monitored on XTLO (pin 11).

# RAM DATA RETENTION—VRR REQUIREMENTS

For the RAM to retain data upon loss of VCC, VRR must be supplied within operating range and RES must be driven low at least eight Ø2 clock pulses before VCC falls out of operating range. RES must then be held low while VCC is out of operating range and until at least eight Ø2 clock cycles after VCC is again within operating range and the internal Ø2 oscillator is stabilized. VRR must remain within VCC operation range during normal R6500/1 operation. When VCC is out of operating range, VRR must remain within the VRR retention range in order to retain data.

#### **TEST LOGIC**

Special test logic provides a method for thoroughly testing the 6500/1. Applying a + 10V signal to the RES line places the 6500/1 in the test mode. While in this mode, all memory fetches are made from Port PC. External test equipment can use this feature to test internal CPU logic and I/O. A program can be loaded into RAM allowing the contents of the instruction ROM to be dumped to any port for external verification.

All 6500/1 microcomputers are tested by Commodore Semiconductor Group using this feature.

#### **MEMORY ADDRESSABLE I/O**

The I/O ports, registers, and commands are treated as memory and are assigned specific addresses. See the system memory map for the addresses. This I/O technique allows the full set of CPU instructions to be used in the generation and sampling of I/O commands and data. When an instruction is executed with an I/O address and appropriate R/W state, the corresponding I/O function is performed.

#### SYSTEM MEMORY MAP

# Notes:

- (1) I/O command only; i.e., no stored data.

- (2) Clears Counter Overflow—Bit 7 in Control Register.

# **ADDRESSING MODES**

#### **Accumulator Addressing**

This form of addressing is represented with a one byte instruction, implying an operation on the accumulator.

# Immediate Addressing

In immediate addressing, the operand is contained in the second byte of the instruction, with no further memory addressing required.

#### **Absolute Addressing**

In absolute addressing, the second byte of the instruction specified the eight low order bits of the effective address while the third byte specifies the eight high order bits. Thus, the absolute addressing mode allows access to the entire 65K bytes of addressable memory.

#### Zero Page Addressing

The zero page instructions allow for shorter code and execution times by only fetching the second byte of the instruction and assuming a zero high address byte. Careful use of the zero page can result in significant increase in code efficiency.

# Indexed Zero Page Addressing

(X, Y indexing). This form of addressing is used in conjunction with the index register and is referred to as "Zero Page, X" or "Zero Page, Y." The effective address is calculated by adding the second byte to the contents of the index register. Since this is a form of "Zero Page" addressing, the content of the second byte references a location in page zero. Additionally, due to the "Zero Page" addressing nature of this mode, no carry is added to the high order 8 bits of memory and crossing of page boundaries does not occur.

#### **Indexed Absolute Addressing**

(X, Y indexing). This form of addressing is used in conjunction with X and Y index register and is referred to as "Absolute, X," and "Absolute, Y." The effective address is formed by adding the contents of X and Y to the address contained in the second and third bytes of the instruction. This mode allows the index register to contain the index or count value and the instruction to contain the base address. This type of indexing allows any location referencing and the index to modify multiple fields resulting in reduced coding and execution time.

#### Implied Addressing

In the implied addressing mode, the address containing the operand is implicitly stated in the operation code of the instruction.

#### **Relative Addressing**

Relative addressing is used only with branch instructions and establishes a destination for the conditional branch.

The second byte of the instruction becomes the operand which is an "Offset" added to the contents of the lower eight bits of the program counter when the counter is set at the next instruction. The range of the offset is -128 to +127 bytes from the next instruction.

#### **Indexed Indirect Addressing**

In indexed indirect addressing (referred to as [Indirect, X]), the second byte of the instruction is added to the contents of the X index register, discarding the carry. The result of this addition points to a memory location on page zero whose contents is the low order eight bits of the effective address. The next memory location in page zero contains the high order eight bits of the effective address. Both memory locations specifying the high and low order bytes of the effective address must be in page zero.

### **Indirect Indexed Addressing**

In indirect indexed addressing (referred to as [Indirect, Y]), the second byte of the instruction points to a memory location in page zero. The contents of this memory location is added to the contents of the Y index register, the result being the low order eight bits of the effective address. The carry from this addition is added to the contents of the next page zero memory location, the result being the high order eight bits of the effective address.

#### **Absolute Indirect**

The second byte of the instruction contains the low order eight bits of a memory location. The high order eight bits of that memory location is contained in the third byte of the instruction. The contents of the fully specified memory location is the low order byte of the effective address. The next memory location contains the high order byte of the effective address which is loaded into the sixteen bits of the program counter.

# INSTRUCTION SET—ALPHABETIC SEQUENCE

| ADC  | Add Memory to Accumulator with Carry                         | LDA | Load Accumulator with Memory                 |

|------|--------------------------------------------------------------|-----|----------------------------------------------|

| AND  |                                                              | LDX | Load Index X with Memory                     |

| ASL  | Shift Left One Bit (Memory or Accumulator)                   | LDY | Load Index X with Memory                     |

| ASL  | Shift Left One bit (Memory of Accumulator)                   | LSR | Shift One Bit Right (Memory or Accumulator)  |

| ВСС  | Branch on Carry Clear                                        | Lon | Shift One Bit Right (Memory of Accumulator)  |

| BCS  | •                                                            | NOP | No Operation                                 |

| BEQ  | •                                                            | NO  | 140 Operation                                |

| BIT  |                                                              | ORA | "OR" Memory with Accumulator                 |

| BMI  | Test Bits in Memory with Accumulator  Branch on Result Minus | UNA | OR Memory with Accumulator                   |

| BNE  |                                                              | PHA | Push Accumulator on Stack                    |

| BPL  |                                                              |     |                                              |

| BRK  | Branch on Result Plus                                        | PHP | Push Processor Status on Stack               |

|      |                                                              | PLA | Pull Accumulator from Stack                  |

| BVC  |                                                              | PLP | Pull Processor Status from Stack             |

| BVS  | Branch on Overflow Set                                       | DO! | Datata Oca Bit Lati (Managara Angara datas)  |

| 01.0 | 010                                                          | ROL | Rotate One Bit Left (Memory or Accumulator)  |

| CLC  | . 3                                                          | ROR | Rotate One Bit Right (Memory or Accumulator) |

| CLD  |                                                              | RTI | Return from Interrupt                        |

| CLI  | Clear Interrupt Disable Bit                                  | RTS | Return from Subroutine                       |

| CLV  | 2.2 (2) (2) (2) (2) (2) (2) (2) (2) (2) (2                   |     |                                              |

| CMF  | ,                                                            | SBC | Subtract Memory from Accumulator with Borrow |

| CPX  | ,                                                            | SEC | Set Carry Flag                               |

| CPY  | Compare Memory and Index Y                                   | SED | Set Decimal Mode                             |

|      |                                                              | SEI | Set Interrupt Disable Status                 |

| DEC  | , ,                                                          | STA | Store Accumulator in Memory                  |

| DEX  |                                                              | STX | Store Index X in Memory                      |

| DEY  | Decrement Index Y by One                                     | STY | Store Index Y in Memory                      |

|      |                                                              |     |                                              |

| EOR  | "Exclusive-or" Memory with Accumulator                       | TAX | Transfer Accumulator to Index X              |

|      |                                                              | TAY | Transfer Accumulator to Index Y              |

| INC  | Increment Memory by One                                      | TSX | Transfer Stack Pointer to Index X            |

| INX  | Increment Index X by One                                     | TXA | Transfer Index X to Accumulator              |

| INY  | Increment Index Y by One                                     | TXS | Transfer Index X to Stack Register           |

|      |                                                              | TYA | Transfer Index Y to Accumulator              |

| JMP  | Jump to New Location                                         |     |                                              |

| JSR  | Jump to New Location Saving Return Address                   |     |                                              |

|      |                                                              |     |                                              |

# **INSTRUCTION SET**

# INSTRUCTION SET-OP CODES, Execution Time, Memory Requirements

|    |            |     | INSTRUCTIONS    |      | HAN  | EDIATE | A   | 850LU | TE  | ZER | PAGI  | :  | ACCU   | M.  | IM  | PLIED | Т      | INO | XI | Т   | (MID) | Y   | 7   | PAGE   | 1 |          | 85. I    | 1   | A   | Y ZI     | 7   | BEI | ATIVE | 1   | INT | REC | . 1 | Z. PI    | 128 | ¥      | Cf  | וחומ | TION | 4 60 | ne? |          |

|----|------------|-----|-----------------|------|------|--------|-----|-------|-----|-----|-------|----|--------|-----|-----|-------|--------|-----|----|-----|-------|-----|-----|--------|---|----------|----------|-----|-----|----------|-----|-----|-------|-----|-----|-----|-----|----------|-----|--------|-----|------|------|------|-----|----------|

| 1  | MI EMON    | IIC | OPERATION       | -    | CP   | 14 :   | CF  | 1     | =   | 04  | 14    |    | OP N   | -   | _   |       | # 0    |     |    | _   |       | 377 | -   | 14     | _ |          |          | -   |     | 001 13   |     |     |       |     |     |     |     | 32       |     |        |     |      |      |      |     |          |

| Α  | D          | 0   | 4 - 14 - C -> A | A) ( | 69   | 2 2    | 60  |       | 3   |     |       |    | -      | ++  | 1   | +     | -      | 1 6 | -  | -   | +     | -   | -   | 1      | - |          |          |     |     |          | 3   |     | -     | +   | 7   | +   | -   | +        | +   | -      | _   | _    |      | _    | _   | $\dashv$ |

| A  | N          | D   | A · M → A       |      | - 1  | - 1    | 1   |       | 3   | - 1 | 20 12 | ٠  |        |     | - 1 |       | 2      | 1   |    | 1   |       | 2   |     |        |   |          |          | 3   | 1   |          | - 1 | - [ | 1     |     | -   |     |     |          | 1   |        |     |      | ,    | _    | -   | 1        |

| А  | S          | L   | C-7 0-0         |      |      | " "    |     |       |     |     |       |    | ) J    | 1.1 | ÷   | -     | 1      |     | -  | ľ   |       | ľ   | 1   | h.     |   | 16       | -        | 2   | -   |          | 3   |     |       | - 1 | -1  | 1   |     | 1        |     | - 1    | •   |      |      | _    |     | -        |

| В  | C          | C   | BRANCH ON C : 0 | (2)  |      | - 1    |     |       |     |     |       | ľ  |        | li  | - 1 | - 1   |        |     | 1  |     | 1     |     | 1   | -      | 1 | -        |          | -   | 1   |          |     | 00  | -     | 2   | - 1 |     |     |          | f   | 8      | •   |      |      |      |     |          |

| В  | С          | S   | BRANCH ON C     | 12.  |      | 1      |     |       |     |     |       |    |        |     | ſ   | 1     |        |     |    |     |       |     |     |        |   |          |          |     |     |          | - 1 |     | - 1   | 2   |     |     |     |          |     |        | F)  |      |      |      |     |          |

| 8  | £          | 3   | BRANCH ON 2 1   | 121  | 7    | +      | 1   | 1     |     | 1   | 1     | +  | $^{-}$ | H   | 7   | 1     | $^{+}$ | +   | 1  | +   | +     | t   | 1   |        |   |          | $\dashv$ | +   | +   | $\dashv$ | -   | FO  | -     | 2   | +   | +   | -   | $\dashv$ | 1   | +      | _   | _    | _    | _    | _   |          |

| 8  | 1          | T   | AIM             |      | -    |        | 20  | 4     | 3   | 24  | 3 .   | à  |        |     |     |       |        |     | 1  |     |       |     |     |        |   |          |          | - 1 |     |          |     | -   | -     |     | 1   | Į.  |     |          | -   |        | vi- |      | _    | _    | - A | ۸.       |

| В  | M          | 1   | BRANCH ON N= 1  | 121  | 1    |        | i   |       | İ   | 1   |       |    |        | 1 [ | - 1 | Ţ     | 1      | 1   | L  |     |       |     |     |        |   |          |          |     | - [ |          |     | 30  | 3     | 2   | - 1 |     | - 1 |          |     | - [    |     | -    | 25   | nur  | _   | _        |

| 8  | A.         | Ε   | BRANCH ON Z - 0 | :21  |      |        | İ   |       |     |     |       |    |        | П   |     |       |        |     |    |     |       | i   |     |        |   |          |          | 1   | 1   |          | - 1 | 00  |       | 2   | 1   | 1   | -1  |          |     | - 1    |     |      |      | _    | _   | _        |

| 8  | Р          | Ī   | SHANCH ON N F & | .2-  | Ų    |        |     | ١,    |     | -   |       |    | İ      |     | - ] | 1     |        |     |    |     |       | 1   |     |        |   |          | - 1      |     |     |          | - 1 | 0   |       | 2   |     |     |     |          | - 1 | - 1    | _   |      | _    | -    |     |          |

| 3  | R          | ĸ   |                 |      | Ť    |        | 1   |       | П   | 1   | 7     | 1  |        | П   | 00  | : 1   | ,      | 1   | 1  | 1   | T     | 1   | 1   | $\Box$ |   | $\vdash$ | T        | 7   | Ť   | 1        | +   |     | 7     | 1   | 1   | 1   | 7   | 7        | 1   | 1      | _   | -    | _    | 1    | _   | _        |

| В  | V          | C   | BRANCH ON V = 0 | -21  |      |        |     |       |     | ļ   | - [   |    | Ì      |     |     |       |        |     |    |     |       |     |     |        |   |          | ļ        | 1   |     | - 1      |     | 50  | 2     | 2   | 1   | 1   | - 1 |          | į l |        |     | _    | -    | _    | _   | _        |

| 8  | V          | S   | BRANCH ON V = 1 | 12   |      |        | 1   |       |     |     |       |    |        | Н   |     | 1     |        |     |    |     |       | 1   |     |        |   |          | 1        |     |     |          | - 1 | 70  |       | 2   | J   |     |     | -        | 1   |        |     | _    | -    | _    | _   | -        |

| C  | L          | C   | 0 → C           |      | 1    | 1      |     |       |     |     |       | Į. | ļ      |     | 181 | 3     | ,      | 1   | 1  |     |       |     |     | l      |   |          |          |     | 1   |          |     | ł   |       |     | -   |     |     |          | -   |        | -   | _    | 0    | _    | _   | -        |

| С  | Ĺ          | Э   | ∂→D             |      | . [  | Ų      |     |       |     |     |       |    |        | 1   | 8.0 | 2     | :      | 1   | 1  | 1   | 1     |     |     |        |   |          | -        |     |     | -        | -   | ļ   | - 1   | -   | 1   | 1   | - 1 | - }      | i   | - 1    | -   | -    | = -  |      | 0   | -        |

| 3  | L          | 1   | 0 → .           |      |      |        | Τ   |       | T   | T   | Т     |    |        |     | 5,8 | 2     | 1      |     | T  | 1   | T     |     | Т   |        |   |          |          |     | 1   | $\neg$   | 1   | 7   | 7     | _   | T   | 7   | _   | T        |     | $\neg$ |     | -    | -    | 0    |     |          |

| Ç  | L          | ٧   | 0 → ∨           | -    | - {  |        | ļ   |       |     | 1   |       | ŀ  |        |     | 88  | 2     | 2      |     |    |     | 1     |     |     |        |   |          |          | - 1 |     | 1        |     | - 1 |       | -   |     |     |     |          |     |        | _   |      | 2    |      |     | 0        |

| C  | 1,1        | P   | 4 = 14          | e 10 | 29   | 2 2    | cn  | 1     | 3 ( | 35  | 3 2   | 2  | 1      | Н   | - [ |       | c      | . 6 | 2  | r): | 5     | 2   | 05  | 1      | 2 | DE       | 4        | 3 1 | 9   | 4        | 3   |     |       |     | -   |     | ą.  |          |     |        |     |      |      | _    | _   | -        |

| C  | P          | ×   | < = M           | F    | 0    | 2 2    | EC  | 4     | 3 4 | 4   | 3 :   | 2  |        |     | 1   |       |        |     |    |     |       |     |     |        |   |          |          |     |     |          |     |     | - 1   |     | - 1 | -   |     |          | - 1 |        |     |      |      | _    | =   | -        |

| C  | c          | Y   | A = A           |      | 100  | 3 2    | cc  | 4     | 3 ( | 14  | 3 3   |    | 1      | 1   | 1   | 1     | 1      | 1   | 1  | 1   | 1     | 1   |     |        |   |          | 1        |     | 1   |          |     | 1   | - 1   | - 1 | - 1 | - } |     | j        | 1   | 1      |     |      | ,    | _    | _   | -        |

| ī. | Ε          | 3   | M = 1 → M       |      |      |        | Œ   | ē     | 3   | ô   | 5 .   | T  |        | П   | П   | T     |        |     | T  |     | Г     | 1   | C6  | ŕ.     | 2 | DF       | •        | 3   | 1   | $\neg$   | 1   | T   | 7     | 1   | T   | T   | T   | T        | П   | $\neg$ |     |      | -    | -    | -   | -1       |

| D  | E          | ×   | ! - ! → !       |      |      | -      |     |       |     | 1   | ı     |    |        | ķ   | 14  | 2     |        |     | 1  |     |       |     |     |        |   |          |          |     |     |          |     |     | - 1   |     | 1   | ļ   |     | 1        |     | - [    |     | ٠    | -    | -    |     | - [      |

| D  | Ε          | Υ   | Y - 1 → V       |      | - [. |        |     | П     | -   |     |       |    |        |     | 85  |       |        | 1   | 1  | 1   | ļ     | ľ   |     |        |   |          | ı        |     | 1   |          |     |     | - 1   |     | 1   | i   | 1   | ı        |     | i      |     |      | -    | -    | -   | -        |

| E  | 0          | Q   | : '!-, à        |      | :9   | 2 /    | 473 | 4     | 3 - | 15  | ? :   |    |        |     |     |       | 4      |     | 1. | 5.  | 5     | 2   | 15  | 3      | 2 | 55       | i        | 3   | ١٥١ | 4        | 3   |     | l     | l   | l   | Į   | 4   | - [      | - [ |        |     |      | -    | -    | -   | - [      |

| 1  | N          | C   | M = 1 → M       |      |      | 1      | ŁΕ  | 6     | J   | · Ú | 5     |    |        |     |     |       |        | İ   |    |     |       |     | 56  | ê      | 2 | c.E      | -        | 5   |     | 1        | 1   | - 1 |       |     | -   |     |     |          | 1   |        |     |      | -    |      | -   | -        |

|    | ٠.         | *   | 2 · → ⊀         |      | 1    |        |     |       |     | Т   |       | Т  |        |     |     | T     |        |     |    | Г   | Г     |     | Ī   |        |   |          |          |     | Ī   |          |     | T   |       | 7   |     | 1   |     | T        |     |        |     |      | -    | -    | -   | -1       |

| 1  | N          | Y   | V · · → V       |      |      |        |     |       |     |     |       |    |        |     | 38. |       |        |     |    | 1   |       |     |     |        |   |          |          |     | -   |          |     | J.  |       |     | -   |     | 1   | 1        |     | 1      |     |      | -    | -    | -   | -        |

| J  | <b>V</b> * | Ρ   | JUMP TO NEW LOC |      |      | 1      | :0  | 3     | 3   | - 1 |       |    |        |     |     |       |        |     |    |     |       |     |     |        | j |          |          |     | Ì   |          |     | 1   | 1     | e   | SC. | 5   | 3   |          |     |        | _   | -    | -    | _    | -   | -        |

| J  | S          | E   | JUMP 3UB        | 1    | 4    |        |     | 15    | 3   | 1   | 1     | -  | 1      |     | 1   | 1     | 1      | -   | 1  | 1   | 1     | 1   |     |        |   | 1        | 1        | -   | -   | 1        |     |     | -     | 1   | 1   | - 1 | 1   | - {      | - 1 | 1      | ~   | -    | -    | -    | -   | - }      |

| L  | D          | Α   | !! → 4          |      | .1   | 2 2    | 40  | 4     | 1   | :5  | 1 :   |    |        |     |     |       | 1.     |     |    | ٠.٠ |       |     | 115 | :      |   | F-1      | :        | 3   | 39  | :        | 3   | 1   |       | 1   | 1   |     |     | 1        |     |        |     |      | -    | ~    |     | -        |

|      |      |        |                                            | Γ      | IMN  | EDIATE | A    | BSOLU | TE  | ZER    | PAGE    | T     | ACCUM | 1    | IMP    | LIED  | Т   | (IND | II. | 1   | DND). | Y | Z, F | PAGE   | X   | AB   | s I  | T   | ABS | Y   | 1   | RELAT | TYE | 1     | NOIRE | CT  | Z.     | PAGE | Y   | C  | OND  | וחונ                                            | ON I | COD  | ES  |

|------|------|--------|--------------------------------------------|--------|------|--------|------|-------|-----|--------|---------|-------|-------|------|--------|-------|-----|------|-----|-----|-------|---|------|--------|-----|------|------|-----|-----|-----|-----|-------|-----|-------|-------|-----|--------|------|-----|----|------|-------------------------------------------------|------|------|-----|

| M    | NEMO | HIC    | OPERATION                                  | $\neg$ | 4    | ٠,   : | . 2  | 1:    | #   | CF.    |         |       | 1.1   | 2    |        |       | - 1 | 1.   | 1.2 | 1   | 1.    | : | ٦.   |        | 2   | P    |      | . 1 | cj. | . = | 1:5 | 1.    | =   | QF.   | V     | T = | OP     |      | =   | 1, | E    | c                                               | 1    | 1    |     |

| Ł    | C    | х      | ₩ → 1                                      |        | :.2  | . 1    | Ac   | 1     | 3   | 36     | 2 1     | -     |       | 1    | 1      | 1     | 1   | 1    |     |     |       |   |      | 1      |     | 1    | 1    | F:  | ٤ . | 3   | 1   | T     | T   | 1     | 1     | 1   | Eō     | 4    | 2   | ,  |      | -                                               |      | -    | -   |

| L    | D    | Y      | ₩ → Y                                      |        | -0   | 2 1    | AC   | 4     | 3   | A.1    | 2       | 1     |       | 1    | 1      | -     |     | 1    |     |     |       |   | :    | .1     | 2   | 3/1  | :    | 3   |     |     |     | 1     |     |       |       |     |        |      |     |    |      | -                                               | _    | . =  | -   |

| L    | S    | я      | Ø → (7 <u>5</u> ) → C                      |        |      |        | 45   | •5    | 3   | in     | - 1     | 1.    | .] ]  |      |        | 1     |     |      |     | l   |       |   | -65  |        | 2   | 58   | 7    |     |     |     |     | ĺ     |     | 1     | Ì     |     |        |      | П   | 3  |      | •                                               | _    | -    | -   |

| N    | 0    | P      | NO OPERATION                               | İ      | - 1  |        |      |       |     |        | 1       |       | 11    |      | Α,     |       |     |      |     |     |       |   |      | -1     | - 1 | - 1  |      |     | 1   |     | 1   |       |     |       |       |     |        |      |     | -  | -    | -                                               | -    | -    | -   |

| 0    | R    | А      | A . M - A                                  | - 1    | 20   | 2 :    | 30   | :     | 3   | 35     | 3       |       |       | 1    |        |       | 25  |      |     |     | 4     |   |      | :      |     |      | :    | 1.  | 4 3 | 3   |     |       | 5   | Ť.    | 1     |     | LJ     |      |     | ,  |      | -                                               | -    | -    | -   |

| P    | н    | ۵      | 4-99: \$.14                                | 3      |      |        |      |       |     | $\Box$ | 1       | 1     | 1     | 1    | :4     | 3 .   | 1   |      | 1   | T   | 1     |   |      |        |     | _    | 1    | 1   | T   | 1   | T   | T     | T   |       | 1     |     |        | П    |     | -  | -    | -                                               | -    |      | 14  |

| .5   | н    | D      | = → 1/4 S - 1 →                            | S      |      | 1      |      |       |     |        | -       |       | 1     |      | 18     | 3 :   | 1   | 1    |     |     |       | 1 | 1    |        |     |      |      | 1   | ľ   |     |     |       |     | ì     | 1     | 1   |        |      |     | -  | -    | -0                                              | _    | -    | 11- |

| P    | 1    | i.     | 5 - 1 → 5 50 →                             | A      | - 1  |        |      |       |     |        |         |       | 11    |      | 10     | : :   |     |      |     |     | ١.    |   |      | - 1    | -   |      | - 1  |     |     |     | 1   | 1     |     |       |       |     |        |      | Ü   | ٠  | ٠    | ~                                               | _    | 100  |     |

| D    | 1    | D      | 8 - 1 → 8 110 →                            | 0      | -    |        |      |       |     | - 1    |         |       |       |      | ·      | ; ;   |     | 8    |     | 1   |       |   |      | - 1    | - 1 |      |      |     |     |     |     | 1     |     |       |       |     |        |      |     |    | -81  | EST                                             | OR   | FC.  |     |

| A    | ~    | -      | + 7 0+ C+                                  |        | ļ    |        | , r. | -5    | 3   | 26     | ٤ :     | 1:    | 1:1   | . 1  |        |       | 1   |      | 1   |     |       |   | je.  | F      |     | 35   | - [  | : [ | 1   | 1   |     |       |     |       |       |     | l      | ( )  | IJ  | ,  | ٠    | ٠                                               | _    | _    | i i |

| F    | ,    | S      | 4047 04                                    |        |      |        | ni.  | ri    | 1   | r-n    | 4       |       |       | -    |        | 1     |     |      |     |     | Т     |   | 3.   |        |     | -: 1 | -    |     | T   | Т   | T   | T     | 1   |       | 1     |     | П      | П    | П   |    | ,    | ,                                               | -    | 1 14 | -   |

| P    | T    |        | RIPH NI                                    | - }    | Į    |        |      | İ.    |     |        |         |       |       |      | :e   . | 6 .   |     |      | İ   |     |       | l |      |        | i   | - 1  |      | 1   |     |     | Î   |       |     | 1     | 1     | 1   |        |      |     |    | R    | EST                                             | OR   | E    |     |

| A    | T    | S      | 818.1 278                                  |        | - [  |        |      | l     |     | - 1    | 1       |       | 1     | ,    | 0      | e   1 |     | Ì    |     |     |       | 1 |      | -      |     |      |      |     |     | 1   |     |       | 1   | 1     |       | ,   |        |      |     | -  | -    | -                                               | -    |      | 177 |

| 5    | В    | C      | $A = M = S \rightarrow A$                  | · ];   | F 3  |        | €    | :     | ١.  | 15     | 3 3     | 2     | 1     | - 1  |        |       | E   |      | 1   | F I | 5     | 2 | 55   | 4      | 2   | FE.  | :    | } F | 9 3 | 3   |     |       |     |       |       |     | 11     |      |     |    |      | :3:                                             | -    |      |     |

| S    | E    | C      | '→0                                        | - 1    | - {  |        |      | 1     | 1   |        | 1       | 1     | 1 1   | - 1  | 38     | :   - | :   |      |     |     | 1     |   | 1    | - {    | 1   | 1    | - 1  | +   | 1   | 1   |     | 1     | ł   | 1     | }     |     |        |      | 1   | -  | -    |                                                 | -    |      | 100 |

| S    | Ε    | Ξ      | 1 → 2                                      | -      | 1    | 1      |      |       |     | -      |         |       |       | -    | 8      | : 1   |     |      | 1   |     |       |   | - 1  | - 1    |     | -    | -  - |     |     |     | 1   |       |     |       |       |     |        |      |     | -  | -    | -                                               | _    | . 4  |     |

| S    | Ε    | -      | 1-1                                        |        | 1    |        |      |       |     | $\neg$ | T       |       |       | T    | 8 .    |       |     | T    | 1   |     |       | ī | _i   |        |     | T    | 1    | 1   | T   |     | T   | T     | T   |       |       | П   | $\Box$ |      | П   | -0 | -    | -                                               | 1    | - 24 | 32  |

| S    | T    | ۵      | A → 1.5                                    |        | - 1  | - 1    | 80   | 4     | 3   | 85     | 3 4     | 3     |       |      |        |       | 8   | ri n |     | g.  | 6     | : | 15   | 4      | 2   | gr.  | 5    | 9   | 9 9 | 3   |     |       |     | 1     |       |     |        |      |     | -  | _    | -                                               | -    | 22   | 120 |

| S    | 7    | ,      | < → !!                                     | -      | ļ    |        | 8E   | 4     | 3   | 86     | 3 1     |       | 1     |      |        |       |     |      |     |     |       | 1 |      |        | - 1 |      | - 1  |     |     | 1   |     |       |     |       |       |     | 96     | 4    | 2   | -  | -    | -                                               | _    | _    | -   |

| S    |      | Y      | Y → 1.1                                    | ĺ      | 1    | 1      | 8C   | 4     | 3   | 9.1    | 2 1     | 1     | 11    | - 1  | 1      |       | 1   |      |     | 1   | 1     | Ì | 34   | 2      | 2   | Î    | 1    |     | 1   | 1   | İ   |       |     | 1     | 1     | 1   |        |      |     | -  | -    | -                                               |      | -    | ě   |

| *    | A    | <      | $\Delta \rightarrow \epsilon$              |        |      |        |      |       | 1   | -      |         |       |       |      | A.     | 2 1   |     | 1    |     |     |       |   |      |        |     |      |      |     |     | 1   |     |       |     |       | 1     |     |        |      |     |    | ٠    | B                                               | =    | 1    | _   |

| ī    | A    | V      | À → V                                      |        |      |        | Ī    |       | e A |        |         |       |       | 7    | 8      | 2 1   |     | T    |     | Γ   |       |   |      |        |     |      |      | T   | T   |     | Т   | Т     | Τ   | Т     | Т     |     |        |      |     | ٠  |      | -                                               | -    | -    | -   |

| 7    | S    |        | 5 → 4                                      | - 1    |      |        |      |       |     |        |         |       | 1 1   | 8    | A :    | 2 1   |     |      |     |     | 1     |   | - 1  |        |     |      |      |     | 1   |     |     | 1     |     |       | 1     |     |        | 1    |     |    | ٠    | $- \frac{1}{2} \left( \frac{1}{2} \right)^{-1}$ | -    | -    | -   |

| T    | ×    | 4      | λ → Δ                                      | - l    | - (  | -      |      | ١.    |     |        | -       |       | 1 1   | Į    | A :    | 2 .   | ı [ |      |     |     |       |   |      | - 1    | -1  | - [  | 1    | 1   | Į.  |     |     | ļ     | ļ   | 1     | 1     |     |        |      |     |    |      | -                                               |      | -    | -   |

| T    | *    | 5      | ← S                                        |        | -    |        |      |       |     | 1      | - 1     |       |       |      | 1A .   | 3 .   |     |      |     |     |       |   |      |        | ļ   |      |      |     |     |     |     |       |     |       |       |     |        | 1    |     | -  | -    | -                                               | -    |      |     |

| Ţ    | v    | A      | $\lambda \rightarrow 7$                    |        |      | 1      |      |       |     |        | $\perp$ |       |       | 1    | 18     | 1     |     |      |     |     |       |   |      |        |     |      | 1    |     |     | _[_ |     |       |     |       | L     |     |        |      |     | ٠  | ٠    | 77                                              | _    | -    | -   |

| 7.53 | Δ    | 00 1 1 | O "N" IF PAGE BOUNDRY IS CRO               | SSEC   |      |        |      |       | ,   | -      | NOE     | VV    |       |      |        |       |     |      |     |     |       |   | ٥(   | 00     |     |      |      |     | *   |     | 50  | C. :  | Si. | FOR   | 2     |     | ٠,     |      | *10 |    | ·CL  | ES                                              |      |      |     |

| (2)  | A    | CC 1 T | O "N" IF BRANCH OCCURS TO SA               | AME    | 5:5  | ε      |      |       | 8   |        | NDE     |       |       |      |        |       |     |      |     |     |       | - |      | £- = F | ÷;  |      |      |     | ,   |     |     | ال    |     |       |       |     | =      |      | 1   | 9  | Y TE | S                                               |      |      |     |

| (3)  |      |        | Ó "N" IF BRANCH CCCURS TÓ DI<br>NOT-BORROW | IttEt  | E,1, | T PAC  | Ε    |       | 4   |        |         |       | LATO  |      |        |       |     |      |     |     |       |   | 43   |        |     |      |      |     | - 6 |     |     |       |     | IF IE |       |     |        |      |     |    |      |                                                 |      |      |     |

| (4)  | 100  |        | NOT-BOHHOW<br>CIMAL MODE Z FLAG IS INVALID |        |      |        |      |       |     |        |         |       | bEt.  |      |        |       |     | FES  | )   |     |       |   | -71  | -      |     |      |      |     |     | 1.  |     |       |     | BIT   |       |     |        |      |     |    |      |                                                 |      |      |     |

|      |      |        | ULATOR MUST BE CHECKED FOR                 | LEA    | CR   | ESUL   | 7    |       | 3.5 |        | AL A    | LIPHT |       | 3.40 |        |       | CH  |      |     |     |       |   |      |        |     |      |      |     | 1   | 16  |     | 2.2   |     | 20    | 2     |     |        |      |     |    |      |                                                 |      |      |     |

Note: Commodore Semiconductor Group cannot assume liability for the use of undefined OP Codes

# **SPECIFICATIONS**

# **Maximum Ratings**

| Rating                      | Symbol           | Value       | Unit |

|-----------------------------|------------------|-------------|------|

| Supply Voltage              | VCC              | 0.3 to +7.0 | Vdc  |

| Input Voltage               | V <sub>in</sub>  | 03 to +7.0  | Vdc  |

| Operating Temperature Range | TA               | 0 to +70    | °C   |

| Storage Temperature Range   | T <sub>stg</sub> | -55 to +150 | °C   |

This device contains circuitry to protect the inputs against damage due to high static voltages, however, it is advised that normal precautions be taken to avoid application of any voltage higher than maximum rated voltages to this circuit.

# STATIC D.C. CHARACTERISTICS (V<sub>CC</sub> = 5V + 5%, T<sub>A</sub> = $0^{\circ}$ -70° C)

| Characteristic                                            | Symbol          | Min     | Тур  | Max  | Unit |

|-----------------------------------------------------------|-----------------|---------|------|------|------|

| Power Dissipation (Outputs High)                          | PD              |         | 500  | 1100 | mW   |

| RAM Standby Voltage (Retention Mode)                      | VRR             | 3.5     | _    | VCC  | Vdc  |

| RAM Standby Current (Retention Mode)                      | IRR             | _       | 10   |      | mAdc |

| Input High Voltage (Normal Operating Levels)              | VIH             | +2.0    | _    | VCC  | Vdc  |

| Input Low Voltage (Normal Operating Levels)               | VIL             | -0.3    | _    | +0.8 | Vdc  |

| Input Leakage Current                                     | AT-15-AE        |         |      |      |      |

| V <sub>in</sub> = 0 to 5.0 Vdc                            | <sup>1</sup> IN | _       | ±1.0 | ±2.5 | μAdc |

| RES, NMI                                                  |                 | _       | ±1.0 | _    | μAdc |

| Input High Voltage (XTLI)                                 | VIHXT           | +4.0    | _    | Vcc  | Vdc  |

| Input Low Voltage (XTLI)                                  | VILXT           | -0.3    | _    | +0.8 | Vdc  |

| Input Low Current                                         |                 |         |      |      |      |

| (V <sub>IL</sub> = 0.4 Vdc)                               | IĮL             | _       | -1.0 | -1.6 | mAdc |

| Output High Voltage                                       |                 |         |      |      |      |

| (VCC = min, ILoad = -100 µAdc)                            | Vон             | 2.4     | _    | _    | Vdc  |

| Output High Voltage                                       |                 |         |      |      |      |

| (V <sub>CC</sub> = min)                                   | VCMOS           | VCC-30% | _    | -    | Vdc  |

| Output Low Voltage                                        |                 |         |      |      |      |

| (VCC = min, ILoad = 1.6 mAdc)                             | VOL             | -       | _    | +0.4 | Vdc  |

| Output High Current (Sourcing)                            |                 |         |      |      |      |

| (V <sub>OH</sub> = 2.4 Vdc)                               | ЮН              | -100    | _    | _    | μAdc |

| Output Low Current (Sinking)                              |                 |         |      |      |      |

| (V <sub>OL</sub> = 0.4 Vdc)                               | IOL             | 1.6     | _    | _    | mAdc |

| Input Capacitance                                         |                 |         |      |      | ,    |

| (V <sub>in</sub> - 0, T <sub>A</sub> = 25°C, f = 1.0 MHz) |                 |         |      |      |      |

| PA, PB, PC, PD, CNTR                                      | Cin             | - 1     | -    | 10   | pF   |

| XTLI, XTLO                                                |                 |         | _    | 50   | pF   |

| Output Capacitance                                        |                 |         |      |      |      |

| (Vin - 0, TA = 25°C, f = 1.0 MHz)                         | Cout            | -       | -    | 10   | pF   |

| I/O Port Resistance                                       | RL              | 3.0     | 6.0  | 11.5 | ΚΩ   |

| PA0-PA7, PB0-PB7, PC0-PC7, PD0-PD7, CNTR                  |                 |         |      |      |      |

NOTE. Negative sign indicates outward current flow, positive indicates inward flow.

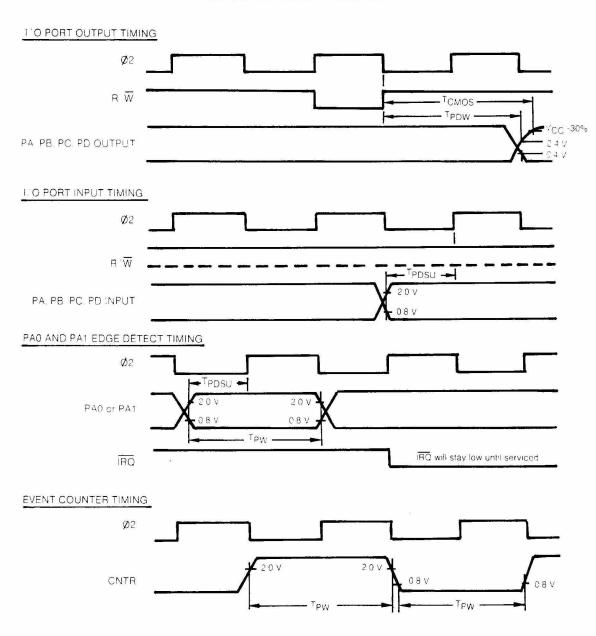

# AC CHARACTERISTICS (VCC = 5 V + 5%, TA = 0° to 70°C)

|                                                |                  | 1 M   | lHz | 2 M   | lHz   | 3 N   | lHz |      |

|------------------------------------------------|------------------|-------|-----|-------|-------|-------|-----|------|

| Parameter                                      | Symbol           | Min   | Max | Min   | Max   | Min   | Max | Unit |

| XTLI Input Clock Cycle Time                    | T <sub>CVC</sub> | 0.500 | 50  | 0.250 | 5.0   | 0.165 | 5.0 | µsec |

| Internal Write to Peripheral Data Valid (TTL)  | TPDW             | 1.0   |     | 0.5   | _     | 0.33  | - 1 | µsec |

| Internal Write to Peripheral Data Vaiid (CMOS) | TCMOS            | 2.0   |     | 1.0   | 1-4-1 | 0.66  | _   | µsec |

| Peripheral Data Setup Time                     | TPDSU            | 400   | _   | 200   | 1999  | 130   | _   | nsec |

| Count and Edge Detect Pulse Width              | TpW              | 1.0   | -   | 0.5   | _     | 0.33  | _   | usec |

# **TIMING CHARACTERISTICS**

# ORDERING INFORMATION

The following information must be provided when ordering:

| Internal Clock Frequency: |                       |              |            |      |

|---------------------------|-----------------------|--------------|------------|------|

| External Frequency Refere | ence:Crysta           | l or Clock _ | RC Network |      |

| Pull-Up Options:          | I/O Port A            | Insert       | Delete     |      |

|                           | I/O Port B            | Insert       | Delete     |      |

|                           | I/O Port C            | Insert       | Delete     |      |

|                           | I/O Port D            | Insert       | Delete     |      |

|                           | CNTR                  | Insert       | Delete     |      |

| Font Verification Media:  | Paper Tap Eprom Other | oe(          | Card Deck  |      |

|                           |                       |              | Spec       | cify |

COMMODORE SEMICONDUCTOR GROUP reserves the right to make changes to any products herein to improve reliability, function or design. COMMODORE SEMICONDUCTOR GROUP does not assume any liability arising out of the application or use of any product or circuit described herein: neither does it convey any license under its patent rights nor the rights of others.