Uart clock has to be 16 times faster than the Baud Rate.

For instance, 19.2 kBaud would require that CLK = 307.2 kHz.

Divider factors for some common crystal/oscillator frequencies:

18.4320 MHz -> : 60 11.0592 MHz -> : 36 9.8304 MHz -> : 32 9.2160 MHz -> : 30 7.3728 MHz -> : 24 6.1440 MHz -> : 20 4.9152 MHz -> : 16 3.6864 MHz -> : 12 2.4576 MHz -> : 8 1.8432 MHz -> : 6

And if the application doesn't require to _exactly_ match the Baud Rate,

there might be some other interesting frequencies...

4 MHz divided by 13 gives 307.6923 kHz, what is ca. 0.16% off from 307.2 kHz.

Note: The UART clock doesn't need to have a 50% duty cycle...

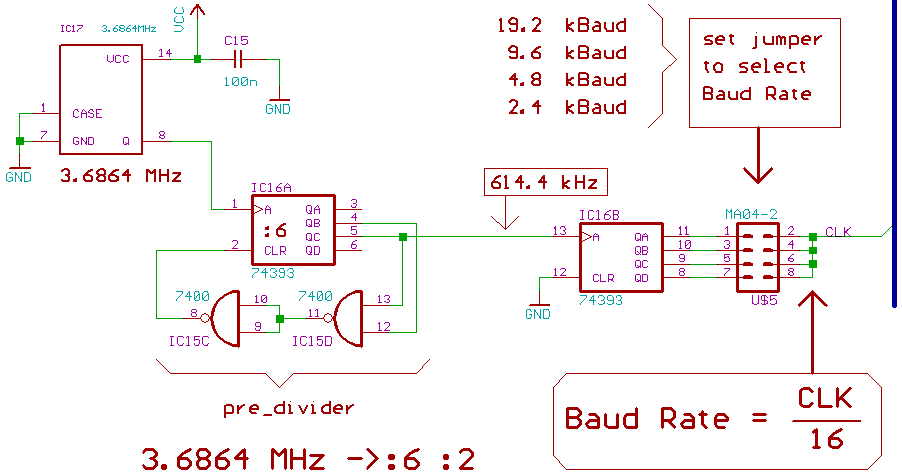

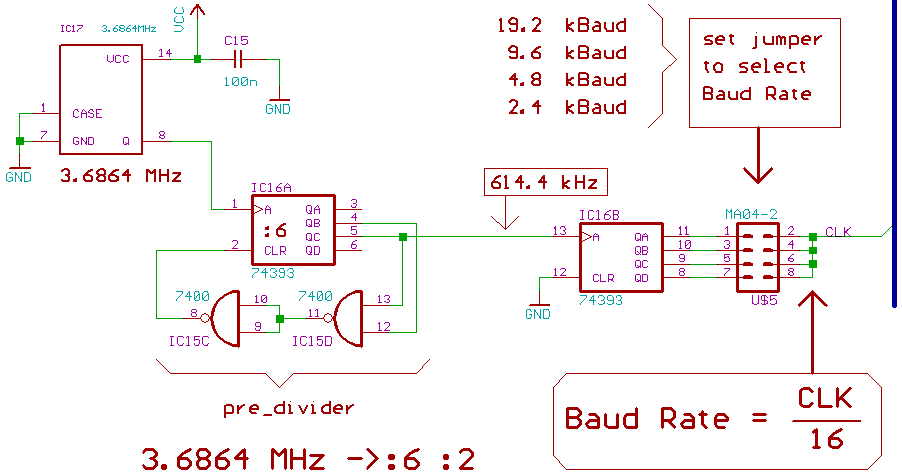

Example for using a 3.6864 MHz TTL oscillator:

It's also possible to build an 8 Bit programmable divider with two 74163.

Another approach would be tapping with a 74151 multiplexer into the

outputs of a 74393, if only a few different Baud Rates are needed.

The most primitive approach is using a jumper to select the Baud Rate,

as shown in the example above.

Also note, that there are a few examples in the Internet about how to

configurate the Baud Rate of UARTs that are integrated into Microcontrollers...

PICs, for instance.

[HOME] [UP]/ [BACK] [1] [2] [3] [4] [5] [6] [7] [8] [9] [NEXT]

(c) Dieter Mueller 2007