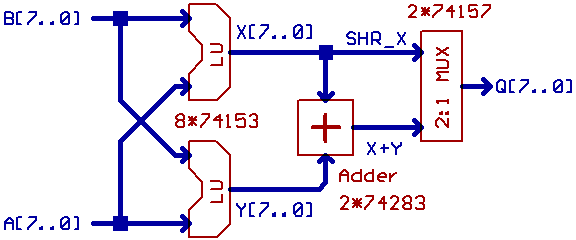

Our latest ALU design:

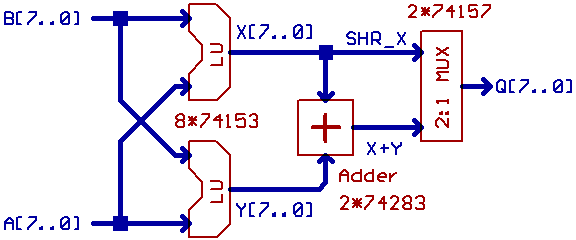

And a close look to the Adder.

The latest ALU design featured two Logic Units,

set between the Adder and the inputs.

Funny thing is, that when we set one Logic Unit to AND,

and the other to OR, the Adder performs out of the results

from the Logic Units a normal addition.

Can we replace the (red marked) Propagate/Generate

OR/AND gates with Multiplexers ?

Or better, with the two Logic Units mountet

in front of the Adder ?

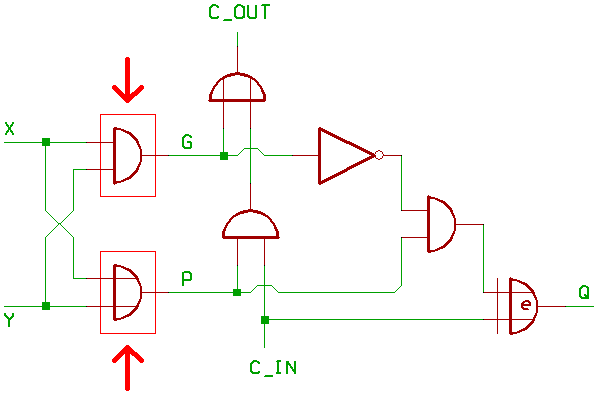

Example. One Bit shown.

It works well.

Logic:

the Generate LU (Logic Unit) produces Zero,

and the Propagate LU is set to the desired logic function.

The Propagate signals are routed to Q.

Carry_input has to be forced to 0.

Not much difference to our previos ALU design.

Left shift:

the Generate LU is set to the desired logic function,

while the Propagate LU is set to the same function or to zero.

The Carry chain will multiply the value by two.

For right shift, we still need a 2:1 multiplexer.

To make the ALU faster, we take the right shift MUX away

from the ALU output, and put it in the Propagate signal path,

between the Propagate LU and the circuitry that forms up Q.

(The Multiplexer will always be faster than the carry chain.)

Arithmetic functions are different:

(Left to right: Generate Control 3..0, Propagate Control 3..0)

1000.1110 // Q=A+B + carry_in

0100.1101 // Q=B-A - /carry_in

0010.1011 // Q=A-B - /carry_in

1010.1111 // Q=A - /carry_in

1100.1111 // Q=B - /carry_in

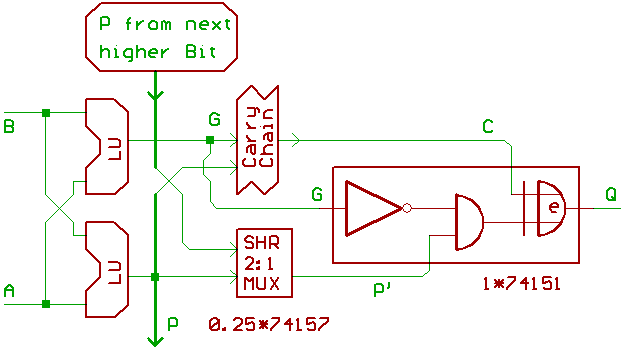

We have to ensure, that we don't unintentionally

increment while shifting right.

When using two different carry_in multiplexers,

one for right shift and one for the carry chain

(74151 recommended), we can replace the circuitry

that generates Q by one 74151 per Bit,

set to a fixed configuration.

Note, that, if you build an 8 Bit CISC CPU,

your status register may end up with two carry flags:

one for data calculation, and one for address calculation

(probably not visible to the "end user").

The low-active 74151 /Q7..0 outputs can be used

together with a 7430 eight_input NAND gate,

for detecting Zero_condition.

When building the carry chain as 8 Bit parallel carry,

using two GAL22V10/7ns, this ALU design could become

faster than the 74F181/74S181.

But we still can simplify this design.

On to part 2.

[HOME] [UP]/ [BACK] [1] [2] [3] [4] [5] [6] [7] [8]

(c) Dieter Mueller 2004