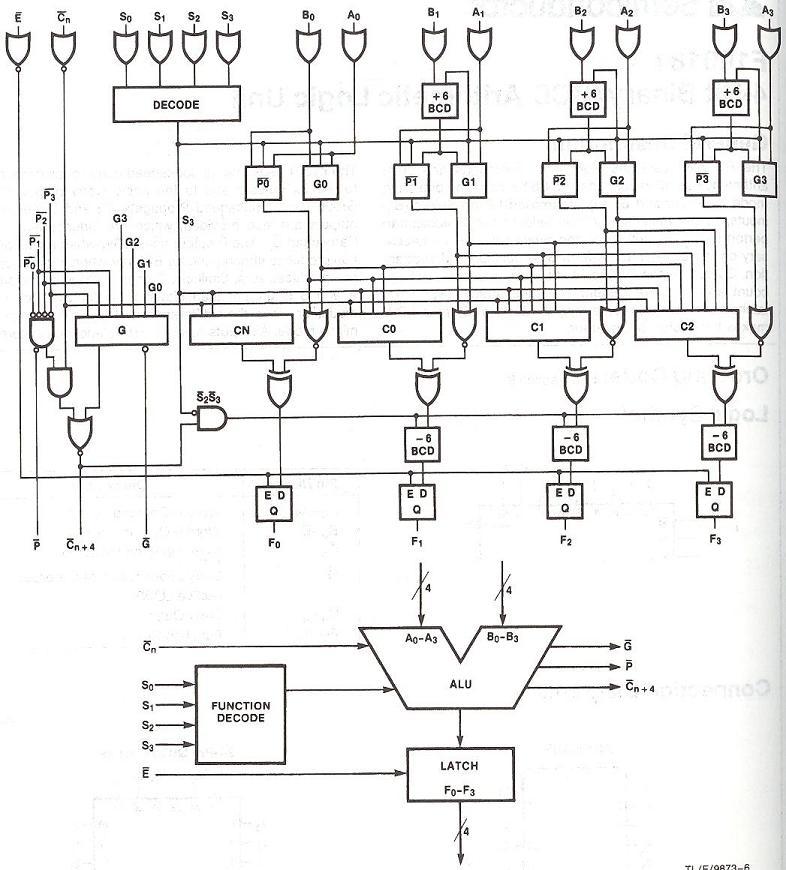

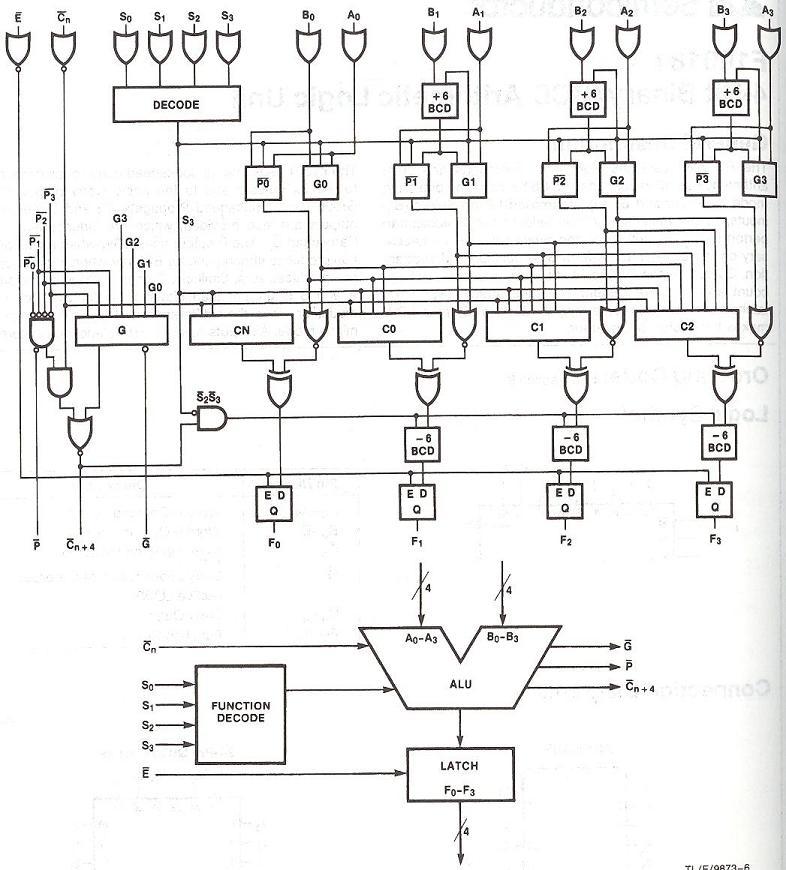

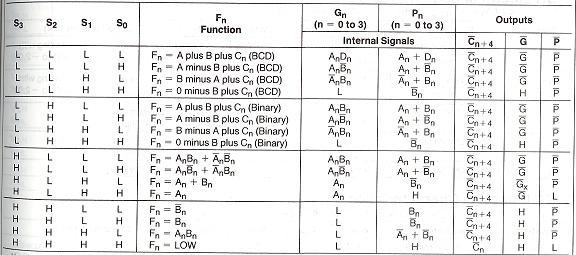

The 100181 ALU (National Semiconductor)

was a 4 Bit ALU which featured BCD arithmetic.

It was ECL, and very different from the 74181.

Unfortunately, the datasheet doesn't go deep enough

into the details of the innards of this IC for my taste.

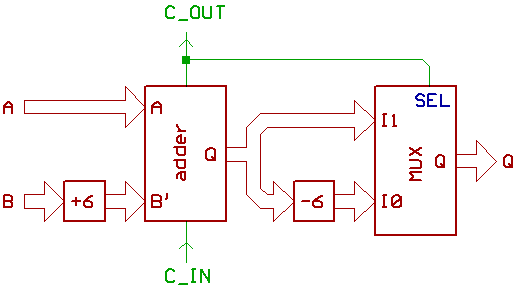

Spent some thoughts about how BCD addition/subtraction

is handled inside this IC, and I don't know if they are correct.

Here we go.

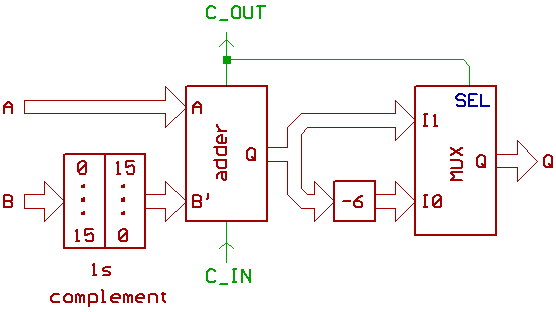

For BCD A+B, the IC adds +6 to B.

So Q=A +B+6.

Means, if A+B is greater than 9, the adder output

A+B+6 is greater than (or equal to) hexadecimal 0x10...

what means that the adder output is a valid 4 Bit BCD number,

and that no BCD correction is necessary.

Downside is, that if A+B is 0..9,

A+B+6 is 6..15, and in that case we have to subtract 6

to turn the adder output into a valid result.

Now for Q=A-B.

C_IN now works as a low_active borrrow.

Let's suppose, that A=9, B=0, C_IN=1.

B' is the 1s complement of B, means decimal 15.

Q=A+B'+C_IN, means Q=9+15+1.

So Q=25... or hexadecimal 0x19.

Means, the 4 Bit binary adder sets the low_active

borrow output to 1, and the adder output turns into 9...

a correct BCD result, so the multiplexer routes the

adder outputs directly to Q.

Suppose, that A=1, B=2, C_IN=1.

Since B is 2 (binary 0010), B' is 13 (binary 1101).

Q=A+B+C_IN, means Q=1+13+1.

So Q=15, and the adder output carry C_OUT is 0.

The output multiplexer then places the -6 circuitry

between adder output and Q... and 15-6=9.

C_OUT=0, since we have a low_active borrow,

so Q is interpreted as -9.

It really works.

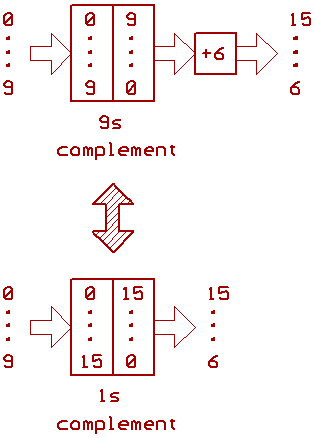

Actually, the 100181 datasheet might tell you a story

that in case of BCD Q=A-B, B is turned into a 9s complement

and then incremented by 6 for generating B'.

But for better readability, I decided to use the

1s complement in my example.

[HOME] [UP]/ [BACK] [1] [2] [3] [4] [5] [6] [7] [8] [NEXT]

(c) Dieter Mueller 2012