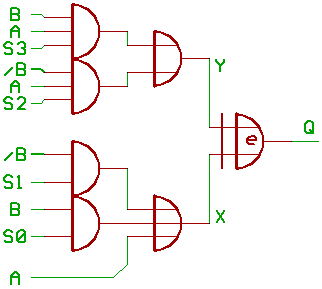

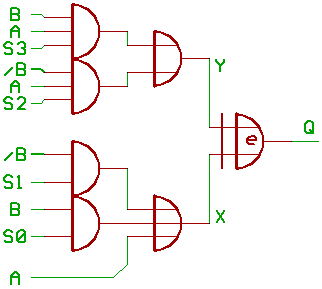

In logic mode, the (internal) carry_outputs

from the carry chain are all forced to 1.

This turns the second XOR into an inverter.

For the first XOR, it doesn't matter if both inputs are high

or low_active... as long as they have the same "polarity".

To simplify things, we imagine them to be high_active.

Now to define, what happens on X,Y:

S3,S2=00: Y=0 S3,S2=01: Y=A&/B S3,S2=10: Y=A& B S3,S2=11: Y=A S1,S0=00: X=A S1,S0=01: X=A| B S1,S0=10: X=A|/B S1,S0=11: X=1 Q=1, if X=Y.

| Q=/(X^Y)= | S3..0 | Y= | X= |

| /A | 0000 | 0 | A |

| A | 1111 | A | 1 |

| /B | 0101 | A&/B | A|B |

| B | 1010 | A&B | A|/B |

| 0 | 0011 | 0 | 1 |

| -1 | 1100 | A | A |

| A| B | 1110 | A | A|/B |

| /A| B | 1000 | A&B | A |

| A|/B | 1101 | A | A|B |

| /A|/B | 0100 | A&/B | A |

| A& B | 1011 | A&B | 1 |

| /A& B | 0010 | 0 | A|/B |

| A&/B | 0111 | A&/B | 1 |

| /A&/B | 0001 | 0 | A|B |

| A^B | 0110 | A&/B | A|/B |

| /(A^B) | 1001 | A&B | A|B |

[HOME] [UP]/ [BACK] [1] [2] [3] [4] [5] [6] [7] [8] [NEXT]

(c) Dieter Mueller 2005